- Jueves, 08 Agosto 2024

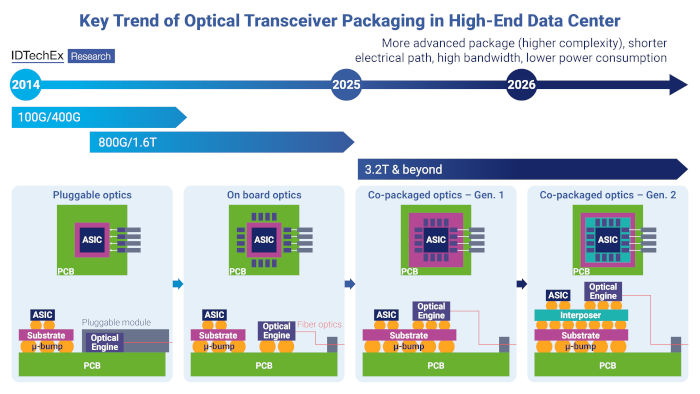

En la última década, la capacidad de los conmutadores Ethernet para centros de datos ha pasado de 0,64 Tbps a 25,6 Tbps, impulsada por la adopción de módulos transceptores ópticos enchufables de 64x400 Gbps o 32x800 Gbps. Sin embargo, estos módulos de alta velocidad, dentro de sus factores de forma actuales, plantean importantes retos. Entre ellos están las densidades necesarias de conectores eléctricos y ópticos, así como el creciente consumo de energía.

En la última década, la capacidad de los conmutadores Ethernet para centros de datos ha pasado de 0,64 Tbps a 25,6 Tbps, impulsada por la adopción de módulos transceptores ópticos enchufables de 64x400 Gbps o 32x800 Gbps. Sin embargo, estos módulos de alta velocidad, dentro de sus factores de forma actuales, plantean importantes retos. Entre ellos están las densidades necesarias de conectores eléctricos y ópticos, así como el creciente consumo de energía.

Para conseguir motores ópticos de nueva generación que soporten 800 Gbps y más por módulo, la velocidad de comunicación debe duplicarse hasta al menos 100 Gbps por carril.

Este aumento introduce importantes problemas de integridad de la señal en el zócalo del conmutador, la placa base y el conector de borde, lo que provoca una mayor disipación de energía en las interfaces SerDes. En la futura conmutación Ethernet, estos problemas de integridad de la señal pueden hacer que el consumo de energía de E/S supere al del núcleo del conmutador. Además, la densidad de integración de los módulos enchufables estándar está limitada por el factor de forma QSFP/OSFP, lo que requiere soluciones avanzadas de gestión térmica que aún no están ampliamente disponibles.

La óptica en coempaquetado (CPO) presenta una solución prometedora a estos retos. A diferencia de los modelos enchufables tradicionales, el CPO integra módulos ópticos directamente en el sustrato ASIC del conmutador, lo que reduce el alcance eléctrico y resuelve eficazmente los problemas de integridad de la señal. Este enfoque ha ganado adeptos entre los principales centros de datos. Sin embargo, la optimización de la estrategia de empaquetado para CPO sigue siendo un tema de continuo debate y desarrollo en el sector. El último informe de IDTechEx, "Co-Packaged Optics (CPO) 2025-2035: Technologies, Market, and Forecasts", explora estos avances en la tecnología CPO y las técnicas de embalaje que permiten su adopción.

La importancia de las tecnologías avanzadas de empaquetado de semiconductores para la óptica empaquetada conjuntamente (CPO)

La integración de CPO en los centros de datos pretende aumentar el ancho de banda de E/S y reducir el consumo de energía. La forma en que se combinan los circuitos integrados fotónicos (PIC) con los circuitos integrados electrónicos (EIC) y los circuitos integrados de conmutación puede influir significativamente en la densidad de ancho de banda de área y de borde, así como en la parasitología del embalaje. Estos factores afectan directamente al ancho de banda de E/S y a la eficiencia energética del transceptor, por lo que una integración inadecuada puede anular las ventajas de la fotónica de silicio.

En el caso de la CPO, la integración de componentes fotónicos y electrónicos puede lograrse mediante diversos métodos, cada uno con ventajas y retos únicos. El más avanzado, y aún en fase de I+D, es la integración monolítica 3D. En ella, los componentes fotónicos se integran en un nodo de proceso electrónico existente con mínimas alteraciones, ubicando la fotónica activa y la electrónica de control en la misma matriz. De este modo se reducen las parásitas y se simplifica el embalaje al eliminar la necesidad de almohadillas de interfaz y protuberancias. Sin embargo, la integración monolítica suele utilizar nodos CMOS más antiguos, lo que se traduce en un rendimiento fotónico subóptimo y un mayor consumo de energía. A pesar de estas limitaciones, ofrece un desajuste de impedancias mínimo y un embalaje simplificado.

Por el contrario, la integración 2D coloca el PIC y el EIC uno al lado del otro en una placa de circuito impreso, conectados mediante enlaces de cables o flip-chip. Este método es sencillo y rentable, pero introduce una inductancia parásita significativa, limitando la E/S agregada debido a las conexiones de un solo borde. Aunque la integración 2D es fácil de empaquetar, la dependencia de las uniones por cable limita el ancho de banda del transceptor y aumenta el consumo de energía, lo que la hace menos eficiente para aplicaciones de alto rendimiento.

La integración híbrida en 3D ofrece una solución más avanzada al colocar el EIC sobre el PIC, a través de diversas tecnologías avanzadas de encapsulado de semiconductores, como TSV (Through-Si-Via), fan-out de alta densidad, unión híbrida Cu-Cu e intercalador fotónico activo, lo que reduce significativamente las parásitas. El uso de tecnologías avanzadas de empaquetado de semiconductores en la integración tridimensional permite un paso denso, lo que mejora el rendimiento. Sin embargo, la disipación térmica sigue siendo un reto, ya que el calor generado por el EIC puede afectar al PIC, lo que requiere soluciones avanzadas de gestión térmica. A pesar de estos problemas térmicos, la integración híbrida 3D consigue un mayor rendimiento gracias a la minimización de las parásitas de embalaje.

La integración en 2,5D sirve como solución intermedia, ya que tanto el EIC como el PIC se encapsulan en un intercalador pasivo con TSV. Este planteamiento mantiene un nivel de parásitos manejable y unas capacidades de paso denso similares a las de la integración 3D, pero añade complejidad con la necesidad de trazas en el intercalador. La integración 2,5D equilibra el rendimiento, el coste y el tiempo de fabricación, pero genera más parásitos que la integración híbrida 3D.

En resumen, cada método de integración presenta ventajas y desventajas en cuanto a rendimiento, complejidad y coste, y su elección depende de los requisitos y limitaciones específicos de la aplicación.

Trayectoria del mercado de la óptica empaquetada conjuntamente (CPO)

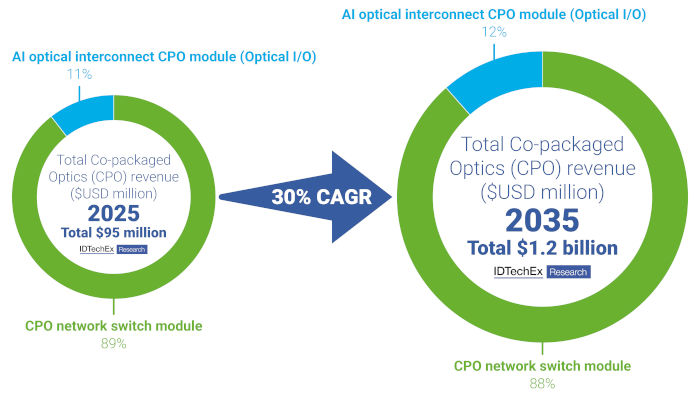

Según IDTechEx, se prevé que el mercado de ópticas empaquetadas conjuntamente (CPO, por sus siglas en inglés) supere los 1.200 millones de dólares en 2035, con un sólido crecimiento interanual del 28,9% entre 2025 y 2035. Se espera que los conmutadores de red CPO dominen la generación de ingresos, impulsados por la posibilidad de que cada conmutador incorpore hasta 16 CPO PIC. Las interconexiones ópticas para sistemas de IA constituirán aproximadamente el 20% del mercado, y cada acelerador de IA utilizará normalmente un PIC de interconexión óptica para satisfacer la creciente demanda de procesamiento y comunicación de datos a alta velocidad en aplicaciones informáticas avanzadas.

El último informe de IDTechEx, "Co-Packaged Optics (CPO) 2025-2035: Technologies, Market, and Forecasts", ofrece una amplia exploración de los últimos avances dentro de la tecnología Co-Packaged Optics. El informe profundiza en las principales innovaciones técnicas y tendencias de envasado, ofreciendo un análisis exhaustivo de toda la cadena de valor. Evalúa a fondo las actividades de los principales actores del sector y ofrece previsiones detalladas del mercado, proyectando cómo la adopción de CPO remodelará el panorama de la arquitectura de los centros de datos del futuro.

Un aspecto central del informe es el reconocimiento del envasado avanzado de semiconductores como piedra angular de la tecnología Co-Packaged Optics. IDTechEx hace especial hincapié en comprender el papel que pueden desempeñar las distintas tecnologías de empaquetado de semiconductores en el ámbito de la CPO.

Autor: Dr. Yu-Han Chang, Analista Principal de Tecnología de IDTechEx