- Lunes, 07 Octubre 2024

En los últimos años, se ha observado una tendencia en la tecnología de transceptores ópticos hacia el acercamiento del transceptor al ASIC. Tradicionalmente, las ópticas enchufables -módulos ópticos que se insertan y extraen del panel frontal de un conmutador- se han situado cerca del borde de la placa de circuito impreso (PCB). Estas ópticas enchufables se utilizan ampliamente en redes de centros de datos para interconectar conmutadores y servidores. Aunque ofrecen flexibilidad, escalabilidad y facilidad de actualización, se enfrentan a importantes retos, sobre todo un elevado consumo de energía y una densidad de ancho de banda limitada.

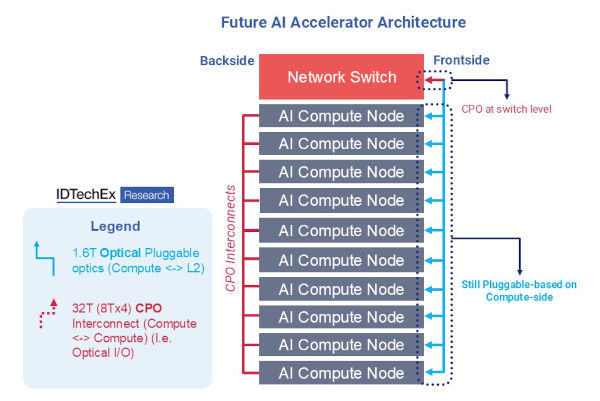

Para superar estas limitaciones, el sector está experimentando un cambio de paradigma. Los transceptores ópticos se están acercando al ASIC, con el objetivo de acortar el canal de cobre necesario para la transmisión de señales eléctricas. Sin embargo, a pesar de los avances en la reducción de la longitud del canal de cobre, los retos que plantea la desviación de la arquitectura enchufable estándar de la industria aún no están totalmente resueltos. En consecuencia, es posible que el sector se dirija directamente hacia soluciones más avanzadas, como la óptica coempaquetada (CPO). El informe de IDTechEx «Co-Packaged Optics (CPO) 2025-2035: Technologies, Market, and Forecasts», explora los últimos avances en tecnología CPO. Analiza las principales innovaciones técnicas y tendencias de empaquetado, evalúa a los principales actores del sector y ofrece previsiones de mercado detalladas, destacando cómo la adopción de CPO transformará la arquitectura futura de los centros de datos.

El auge de la óptica en coempaquetado (CPO)

La óptica coempaquetada (CPO) representa un salto significativo en la tecnología de transmisión de datos. La CPO integra el motor óptico y el silicio de conmutación en el mismo sustrato. Este diseño elimina la necesidad de que las señales atraviesen la placa de circuito impreso, lo que reduce aún más la ruta del canal eléctrico y mejora significativamente el rendimiento.

La reducción de la ruta del canal eléctrico es crucial porque el núcleo de la transferencia de datos depende del circuito SerDes (serializador/deserializador) basado en cobre, que conecta el ASIC de conmutación a los transceptores enchufables. A medida que crece la demanda de datos, la tecnología SerDes ha evolucionado para permitir una transmisión más rápida, pero los ASIC más rápidos requieren mejores conexiones de cobre, ya sea a través de más canales o velocidades más altas. Sin embargo, a medida que aumentan la densidad de enlaces y el ancho de banda, una parte significativa de la potencia del sistema -y, por tanto, del coste- se consume en conducir las señales desde el ASIC hasta las interconexiones ópticas en el borde del rack. Las limitaciones de tamaño de los paquetes BGA (ball grid array) de los ASIC, debidas a problemas de alabeo, exigen mayores velocidades de SerDes para soportar un mayor ancho de banda. Sin embargo, esto también se traduce en un mayor consumo de energía, ya que a frecuencias más altas se producen mayores pérdidas de canal.

Una de las soluciones clave a estos retos es reducir la distancia entre el ASIC y el transceptor óptico. Una parte importante de la energía del sistema se consume en conducir las señales de datos desde el ASIC hasta las interconexiones ópticas en el borde del rack. Acercar los transceptores ópticos al ASIC ofrece varias ventajas:

Reducción de las pérdidas de señal: Al acortar la ruta eléctrica entre el ASIC y la interconexión óptica se minimiza la degradación de la señal.

Menor consumo de energía: La reducción de la distancia permite el uso de opciones SerDes de menor potencia, lo que se traduce en un menor consumo general del sistema.

Mayor eficiencia y rendimiento: Al reducir la potencia necesaria para la transmisión de datos, la eficiencia y el rendimiento del sistema mejoran significativamente.

Escalabilidad: La tecnología CPO admite la escalabilidad futura de los sistemas de gran ancho de banda, lo que la hace ideal para los centros de datos que necesitan satisfacer la creciente demanda de datos.

Cómo el CPO dará forma a la arquitectura de interconexión para la IA

El CPO está llamado a transformar la arquitectura de interconexión para la IA. En este artículo, IDTechEx utiliza el vanguardista servidor DGX NVL72 de Nvidia como ejemplo para explicar cómo IDTechEx predice la arquitectura de IA de próxima generación. Nvidia, el líder del mercado en aceleradores de IA, ha diseñado el DGX NVL72 para redefinir los estándares de rendimiento de la IA, soportando hasta 27 billones de parámetros, superando con creces los 1,5 billones de parámetros de ChatGPT 4.

El DGX NVL72 contiene 18 nodos de cálculo, cada uno equipado con cuatro GPU Blackwell y dos CPU Grace, junto con nueve conmutadores NVLink. Las arquitecturas de aceleradores de IA modernas, como ésta, emplean múltiples redes de comunicación para gestionar el flujo de datos:

Backside Compute Network: En la arquitectura DGX NVL72, cada nodo de computación se conecta a un conmutador de computación L1 a través del NVLink Spine de Nvidia, una interconexión de cobre de alta velocidad que ofrece un ancho de banda bidireccional de 1,8T a través de 18 carriles de 100G, utilizando 36 hilos de cobre por conexión. Los conmutadores L1 están interconectados de forma similar, lo que supone un total de 5.184 hilos de cobre en todo el sistema. Para mantener la integridad de la señal a estas distancias, se utilizan retemporizadores en los conmutadores, aunque introducen limitaciones de latencia y ancho de banda, especialmente a velocidades más altas como 100G por carril. Además, este tipo de enlaces de cobre, aunque rentables, se enfrentan a problemas de degradación de la señal, como la pérdida de canales y la fluctuación del reloj en distancias largas, que se acentúan a medida que aumenta la demanda de ancho de banda.

Las interconexiones ópticas presentan una alternativa convincente al cobre, ya que ofrecen una densidad de ancho de banda mucho mayor y una mayor eficiencia en largas distancias, algo fundamental para las cargas de trabajo de IA que implican transferencias masivas de datos entre GPU. De cara al futuro, se espera que las interconexiones de cobre sean sustituidas por las ópticas coempaquetadas (CPO), que permitirán conexiones directas entre nodos de cálculo y eliminarán la necesidad de conmutadores de cálculo L1 en la red trasera.

En última instancia, la CPO remodelará la arquitectura de interconexión de la IA mejorando el movimiento de datos, reduciendo los cuellos de botella y permitiendo una mayor eficiencia y escalabilidad en los sistemas de IA de próxima generación. Es probable que en el futuro veamos conexiones ópticas directas, eliminando los conmutadores de computación y aumentando el ancho de banda para las cargas de trabajo de IA, aunque también aumentará la complejidad de las conexiones.

Un aspecto central del informe es el reconocimiento del empaquetado avanzado de semiconductores como piedra angular de la tecnología de óptica coempaquetada. IDTechEx hace especial hincapié en comprender el papel que pueden desempeñar las distintas tecnologías de empaquetado de semiconductores en el ámbito de la CPO.

Autor: Dr. Yu-Han Chang, analista tecnológico principal de IDTechEx